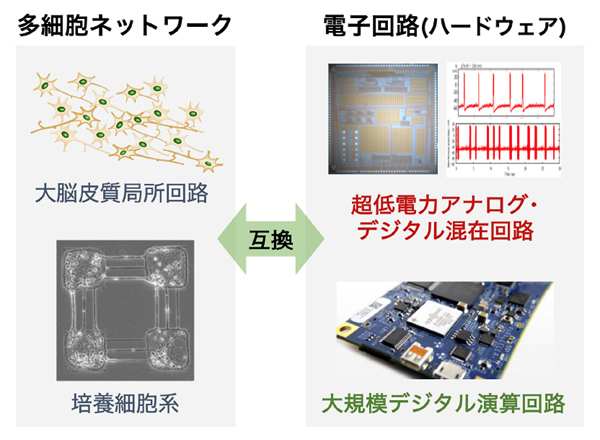

文部科学省 科学研究費助成事業 「学術変革領域研究(A)」

ハードウェア応用班(A04)

A04-1 多細胞神経ネットワーク情報処理のアナログ・デジタル回路実装

代表河野 崇東京大学 生産技術研究所 教授Researchmap

協力小林 正治東京大学 生産技術研究所 准教授Researchmap

達成目標

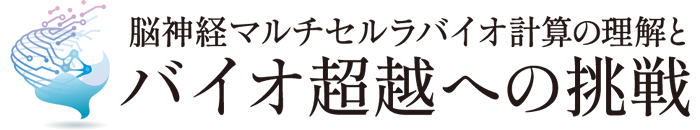

多細胞ネットワーク上の情報処理の効率的なハードウェア実装方法の確立を目的として、超低電力回路基盤としてアナログ・デジタル混在集積回路を開発すると共に、専用デジタル演算回路によるプロトタイピングも実施する(右図)。

具体的計画

マルチセルラネットワークの情報処理をリアルタイム(以上)の速度で再現し、バイオ素子に迫るエネルギー効率を達成できる電子回路を実現する。これは、神経細胞の電気活動を再現するニューロン回路と、シナプス伝達と可塑性とを再現するシナプス回路とで構成される電子回路版神経ネットワーク(シリコン神経ネットワーク(SiNN))である。SiNNは現行AIの低電力実行ハードウェア(ニューロモルフィックハードウェア)として注目されているが、人工ニューラルネットワークと同等の処理に特化した極度に簡略化されたモデルが採用されており、マルチセルラネットワークの電気活動は再現できない。本研究では、カルシウムベース可塑性モデルやA01松井班、A03神谷班の研究成果など最新の実験脳科学の知見を取り込むことで生物規範性を高め、マルチセルラネットワークの機能を再現できるSiNN回路を開発する。神経細胞と同等の電圧・コンダクタンスレンジで動作する新しい超低電力アナログ回路技術を開発し、定性的神経モデリングと組み合わせることで生体神経ネットワークと同等のエネルギー効率での動作を目指す。このような回路では神経細胞の物理ノイズに起因する自発活動を容易に再現できるため,本研究領域の達成目標の一つである、ノイズによる自発活動を許容する超低消費電力脳型システムのハードウェア基盤に適合する。アナログSiNN集積回路の開発、試作に加え、マルチセルラネットワークのFPGAデジタル回路によるプロトタイピングも行う。これにより,A01松井班の推定する大脳皮質局所回路の機能的結合構造の実装や、A02山本班の人工神経細胞回路の再現、A04平田班のロボット制御への応用を可能とする。

ハードウェア基盤の創成

A04-2 生物規範的情報処理モデルの実機実装と適応制御

代表平田 豊中部大学 理工学部 教授Researchmap

分担奥野 弘嗣大阪工業大学 情報科学部 准教授Researchmap

分担安川 真輔九州工業大学 大学院生命工学研究科 准教授Researchmap

達成目標

生物脳を規範とした感覚運動学習モデルをFPGAに実装し、これをコントローラとするロボット適応制御を通して、現行の制御手法に対する利欠点を明らかにすると同時に、身体性を有するマルチセルラ情報処理システムから創発する現象を実証・評価する。

具体的計画

領域内の他の班で構築されるものを含め,マルチセルラ系の感覚運動学習を記述した数理モデルをリアルタイム動作可能な形でFPGAに実装し、実世界におけるロボット制御(多種感覚入力に対する運動出力制御)実験を実施する。特に、動物の脳機能の最も顕著な特徴の1つである自発活動と、それによる予測的な運動制御を適応的に獲得する過程を評価する。研究期間の後半には、領域内連携により、細胞とロボットをつなぐインターフェースを構築し、人工神経細胞回路をコントローラとするロボット適応制御技術を開発する。これらを通じて、身体性を有するマルチセルラバイオ計算モデルが実世界の多感覚情報と相互作用することにより創発する種々の現象を明らかにする。

実機制御実験スキーム(下)

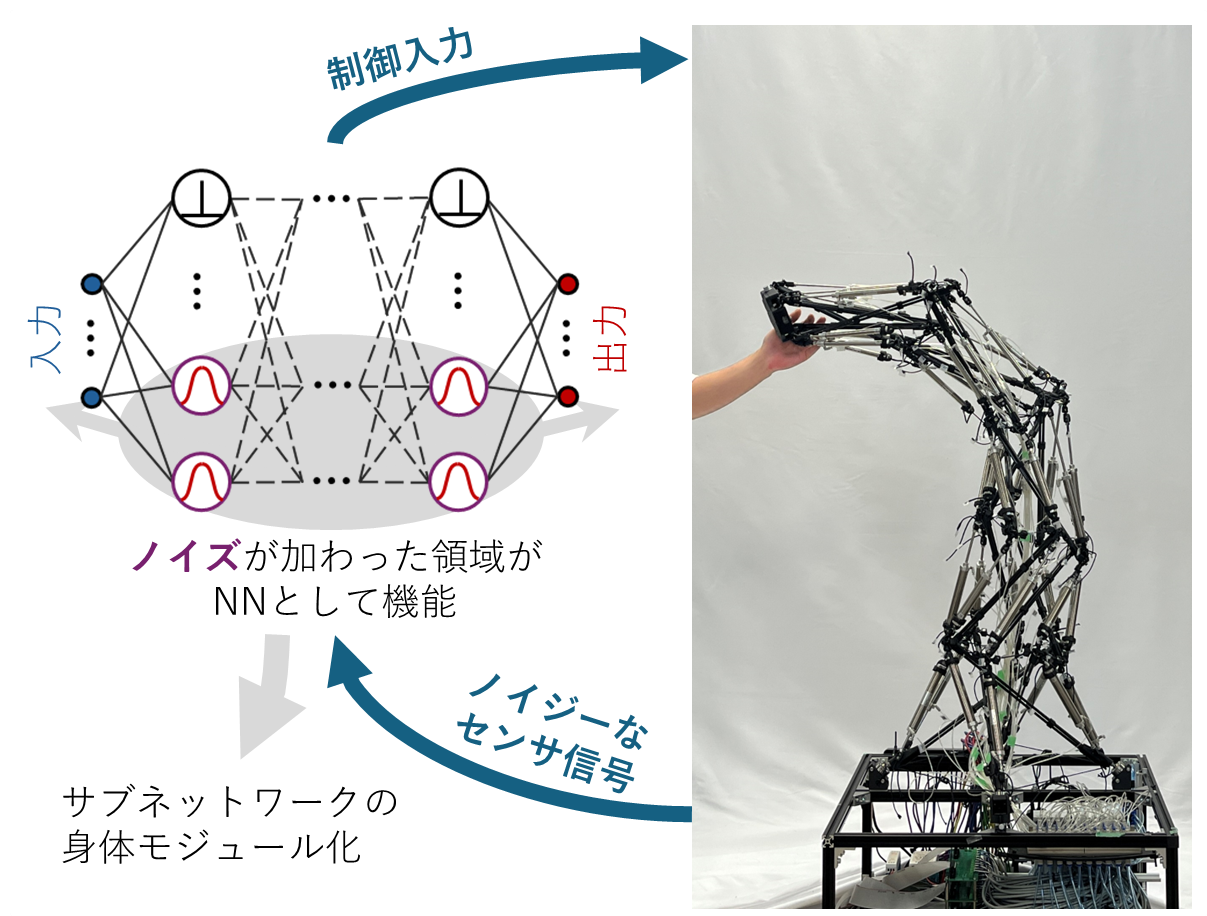

A04-3a ノイズで機能化される神経回路モデルによる冗長ロボットの身体モジュール学習

代表池本 周平九州工業大学 大学院生命体工学研究科 准教授Researchmap

達成目標

ノイズが加わることで学習・推論が可能になるニューラルネットワークで冗長マニピュレータの運動学習を行うことで、身体部位に依存したノイズの存在が,身体部位ごとの制御に関わるサブネットワークを自己組織的に形成することを示す。

具体的計画

一般に、ニューラルネットワークのパラメータはユニットの並び順による冗長性を持つ。そのため、ヒトの脳のような機能局在は起こらず、近しいユニットのグループは必ずしも近しい機能を持たない。本研究では、確率共鳴によって学習・推論が可能になるニューラルネットワークを冗長マニピュレータの運動学習に用いることで、近しい身体部位から得られる感覚信号やノイズが、機能局在を形成するための自然なバイアスになり得ることを示す。まず、ロボットシステムで広く使われるミドルウェアであるROS 2を用い、確率共鳴を利用するニューラルネットワークと冗長マニピュレータの両方をノードとして扱えるようにすることで、本研究および領域内連携の基盤を整える。リーチング等のシンプルなタスクを例に運動学習を行い、この作業仮説の妥当性を示すとともに、領域内連携による成果拡大を図る。

A04-3b 環境熱ゆらぎ誘起確率共鳴スピン波による脳模倣情報処理素子

代表田畑 仁東京大学 大学院工学系研究科(工学部) 教授Researchmap

達成目標

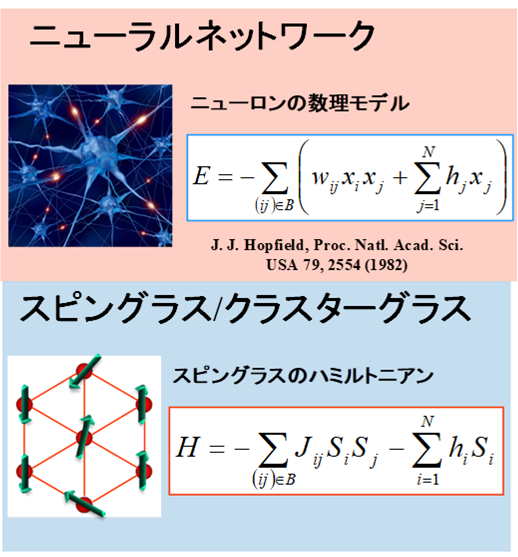

革新的なコンピューティング技術の創生に向けて、低エネルギー(消費電力)動作を可能とする室温動作可能なスピングラス材料を開発し、それを用いた環境熱ゆらぎ誘起確率共鳴スピン波脳模倣情報処理デバイスを創製する。

具体的計画

(1)革新的低消費電力スピン材料として、情報伝達・処理に電子の輸送を伴わずジュール熱損失が回避可能な、スピン角運動量(スピン波)伝搬特性に優れた材料を開発。

(2)生体ゆらぎに学ぶことで、従来厄介者であった“熱ゆらぎ”を環境からのエネルギー源として積極的に活用する常温動作可能なスピンゆらぎ材料(スピングラス)創製。

(3)環境熱ゆらぎに触発される確率共鳴原理に基づくスピン波デバイスを開発する。

これらにより、生物機能に学んだ逆転の発想で“環境熱ゆらぎ誘起の確率共鳴による低エネルギー動作可能な脳機能模倣素子”の開発を目指す。

A04-3c デジタル脳細胞スパイクインタフェースによるウェット・ハード積層ハイブリッドウェア

代表三浦 典之大阪大学 大学院情報科学研究科 教授Researchmap

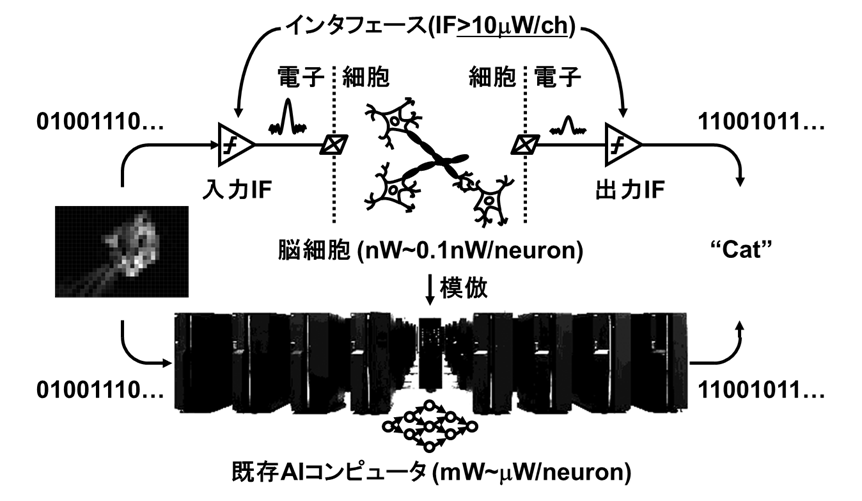

達成目標

生体脳細胞ネットワークを情報処理装置とするウェットウェアをシリコン集積回路ハードウェア上に積層集積したウェット・ハード積層ハイブリッドウェアの低消費電力実装を目標に、両者を高効率につなぐ専用デジタル脳細胞スパイクインタフェースを開発する。

具体的計画

(1)脳細胞ネットワークにおける有効な情報表現形式であるスパイク発火の有無の挿入と検知に特化した専用デジタル脳細胞スパイクインタフェースの低電力回路構成法を明らかにする。

(2)インタフェースアレイを介してアクセスできるデジタル離散化された脳細胞ネットワークの時空間ダイナミクスを情報処理機能化する高効率の入出力層デジタル信号処理方式を明らかにする。

(3)最終的に、(1-2) の技術を組み込んだ積層ハイブリッドウェアのプロトタイプを実装し、既存の脳模倣型シリコン人工知能に対する情報処理エネルギー効率における超越性の実機実証を目指す。